High-speed serial bus architectures are the norm in today's high-performance designs. While parallel bus standards are undergoing some changes, serial buses are established in multiple markets and devices: computers, cell phones, entertainment systems, and more. Serial buses offer performance advantages and design simplification (fewer traces) in circuits and board layouts. Serial data links function as the arteries of today's informational world, transferring data from one point to another in a processing system. To ensure accurate delivery and reception of data in a digital system, data is governed by Clock and Data Recovery (CDR) circuits, which act as the handshake in the data system. The key to accurate data reception and interpretation is specifically related to knowing exactly "where" a clock edge is at any given time.

Since transmitting and receiving devices can be anywhere from the same desk to the other side of the world, there are influences in each different location or environment that can affect how a clock edge travels from the time the data is sent to the time it is received and interpreted by a device. These influences are varied and include temperature, physical motion/vibration, and even the architecture of the original clock signal. The net result is either accurate data or not, and clearly “no” is never an option in any system. For end users, this can mean poor quality of experience and disruption of internet sessions and related services (such as poor voice quality on calls or video conferences).

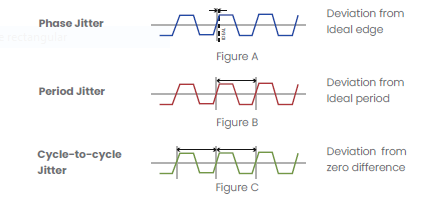

In summary, jitter (variation in data arrival time) is a critical factor in the design of high-performance systems. Engineers must carefully consider how to minimize jitter to ensure data integrity and reliability in increasingly connected and demanding environments. Clock accuracy and synchronization are critical to the smooth operation of critical systems in today's industry.

Serial Buses in Modern Designs