高速串行总线架构是当今高性能设计的常态。虽然并行总线标准正在发生一些变化,但串行总线已在多个市场和设备中建立:计算机、手机、娱乐系统等。串行总线在电路和电路板布局中提供性能优势和设计简化 (走线更少)。串行数据链路充当当今信息世界的动脉,在处理系统中将数据从一个点传输到另一个点。为了确保在数字系统中准确传输和接收数据,数据由时钟和数据恢复 (CDR) 电路控制,这些电路充当数据系统中的握手。准确接收和解释数据的关键与准确了解 clock edge 在任何给定时间的 “位置” 有关。

由于发送和接收设备可以位于从同一台到世界另一端的任何地方,因此每个不同的位置或环境中都存在影响因素,这些影响会影响 clock edge 从数据发送到设备接收和解释数据的方式。这些影响是多种多样的,包括温度、物理运动/振动,甚至原始 clock 信号的架构。最终结果要么是准确的数据,要么不是准确的,显然,在任何系统中,“不”都不是一个选项。对于最终用户来说,这可能意味着体验质量差以及 Internet 会话和相关服务的中断(例如通话或视频会议的语音质量差)。

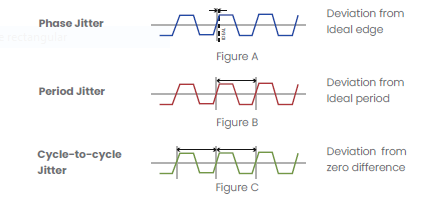

总之,抖动(数据到达时间的变化)是高性能系统设计中的一个关键因素。工程师必须仔细考虑如何最大限度地减少抖动,以确保在日益互联和要求苛刻的环境中的数据完整性和可靠性。时钟精度和同步对于当今工业中关键系统的平稳运行至关重要。

现代设计中的串行总线